# DIPORT CONTROLLER Specification VERSION Draft (16.Sept.2022)

EDITOR(S):

Gary Miller, NXP

# **Executive Summary**

The diPort controller (diPort) is intended to provide a scalable chiplet interface controller for use with IO coherent accelerators. diPort is intended to add runtime processor communication and signaling between two die via designated serial and parallel interface protocols.

DiPort is optimized for die-to-die communications and serves as an ecosystem for Systems-in-Package. It enables automatic configuration of communication at start-up. The connected die appears to software as on-die resources using built-in memory map address translation. Error detection, corruption prevention and resiliency are supported.

This initial specification captures NXP diPort content, which supports a virtual interconnection of an AXI bus between two die, as well as signaling of discrete information between die. IO coherent support (e.g., ACE-lite) will be added in the next specification release. The diPort controller is, however, intended to interface with any on-die bus definition to provide a virtual connection between die.

# **About Open Compute Foundation**

The Open Compute Project Foundation is a 501(c)(6) organization which was founded in 2011 by Facebook, Intel, and Rackspace. Our mission is to apply the benefits of open source to hardware and rapidly increase the pace of innovation in, near and around the data center and beyond. The Open Compute Project (OCP) is a collaborative community focused on redesigning hardware technology to efficiently support the growing demands on compute infrastructure. For more information about OCP, please visit us at http://www.opencompute.org

# Contents

| 1 | Lice   | nse                                     | 6  |

|---|--------|-----------------------------------------|----|

|   | 1.1 00 | CP CLA                                  | 6  |

|   | 1.2 Ac | knowledgements                          | 6  |

| 2 | Rev    | ision Table                             | 7  |

| 3 | Glos   | ssary                                   | 8  |

| 4 | Intro  | oduction                                | 8  |

|   | 4.1    | Block Diagram                           | 9  |

|   | 4.2    | Features                                | 13 |

|   | 4.3    | Operating Modes                         | 13 |

|   | 4.3.   | 1 Disabled Mode                         | 13 |

|   | 4.3.2  | 2 BIST Mode                             | 7  |

|   | 4.3.3  | Normal Mode                             | 7  |

| 5 | diPo   | ortSD register descriptions             | 7  |

|   | 5.1    | diPortSD memory map                     | 7  |

|   | 5.2    | Error and Control Register (ECR)        | 9  |

|   | 5.3    | Quality Of Service (QOS)                | 12 |

|   | 5.4    | Signaling Enable (SIGEN)                | 13 |

|   | 5.5    | Signaling Delay (SIGD)                  | 14 |

|   | 5.6    | Elasticity Buffer Configuration (EBCFG) | 15 |

|   | 5.7    | Logical Address Region 0 (LAR0)         | 16 |

|   | 5.8    | Physical Address Region 0 (PAR0)        | 17 |

|   | 5.9    | Region Size 0 (RS0)                     | 18 |

|   | 5.10   | Logical Address Region 1 (LAR1)         | 19 |

|   | 5.11   | Physical Address Region 1 (PAR1)        | 20 |

|   | 5.12   | Region Size 1 (RS1)                     | 21 |

|   | 5.13   | Logical Address Region 2 (LAR2)         | 23 |

|   | 5.14   | Physical Address Region 2 (PAR2)        | 24 |

|   | 5.15   | Region Size 2 (RS2)                     | 25 |

|   | 5.16   | Logical Address Region 3 (LAR3)         | 27 |

|   | 5.17   | Physical Address Region 3 (PAR3)        | 28 |

|   | 5.18   | Region Size 3 (RS3)                     | 29 |

|   | 5.19   | Logical Address Region 4 (LAR4)         | 31 |

|   | 5.20   | Physical Address Region 4 (PAR4)        | 32 |

|   | 5.21   | Region Size 4 (RS4)                     |    |

|   | 5.22   | Logical Address Region 5 (LAR5)         | 35 |

|   | 5.23   | Physical Address Region 5 (PAR5)        | 36 |

|   | 5.24   | Region Size 5 (RS5)                     | 37 |

| Open C | Compute Project - diPort Controller Specification Draft | 4  |

|--------|---------------------------------------------------------|----|

| 5.25   | Logical Address Region 6 (LAR6)                         | 39 |

| 5.26   | Physical Address Region 6 (PAR6)                        | 40 |

| 5.27   | Region Size 6 (RS6)                                     | 41 |

| 5.28   | Logical Address Region 7 (LAR7)                         | 43 |

| 5.29   | Physical Address Region 7 (PAR7)                        | 44 |

| 5.30   | Region Size 7 (RS7)                                     | 45 |

| 5.31   | Logical Address Region Upper 0 (LARU0)                  | 47 |

| 5.32   | Physical Address Region Upper 0 (PARU0)                 | 48 |

| 5.33   | Logical Address Region Upper 1 (LARU1)                  | 49 |

| 5.34   | Physical Address Region Upper 1 (PARU1)                 | 50 |

| 5.35   | Logical Address Region Upper 2 (LARU2)                  | 50 |

| 5.36   | Physical Address Region Upper 2 (PARU2)                 | 51 |

| 5.37   | Logical Address Region Upper 3 (LARU3)                  | 52 |

| 5.38   | Physical Address Region Upper 3 (PARU3)                 | 53 |

| 5.39   | Logical Address Region Upper 4 (LARU4)                  | 53 |

| 5.40   | Physical Address Region Upper 4 (PARU4)                 | 54 |

| 5.41   | Logical Address Region Upper 5 (LARU5)                  | 55 |

| 5.42   | Physical Address Region Upper 5 (PARU5)                 | 56 |

| 5.43   | Logical Address Region Upper 6 (LARU6)                  | 56 |

| 5.44   | Physical Address Region Upper 6 (PARU6)                 | 57 |

| 5.45   | Logical Address Region Upper 7 (LARU7)                  | 58 |

| 5.46   | Physical Address Region Upper 7 (PARU7)                 | 59 |

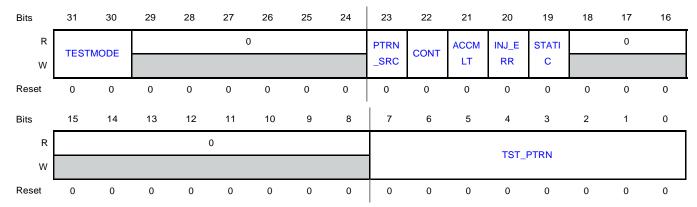

| 5.47   | BIST Control and Pattern (BIST_CP)                      | 59 |

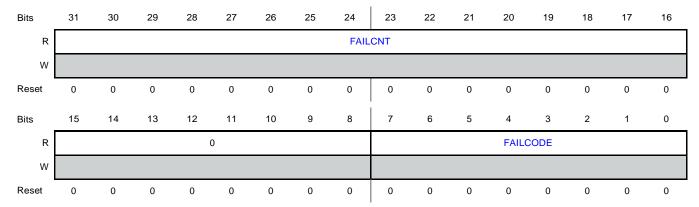

| 5.48   | BIST Status (BIST_ST)                                   | 61 |

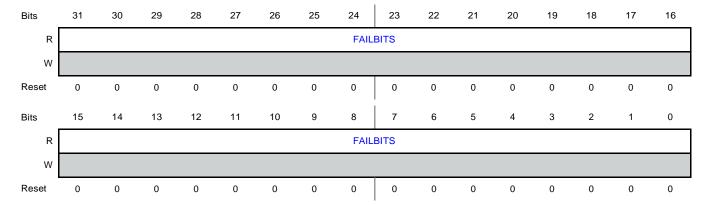

| 5.49   | BIST Failures (BIST_FLS)                                | 62 |

| 5.50   | BIST Upper Failing Data (BIST_UFD)                      | 63 |

| 5.51   | BIST Lower Failing Data (BIST_LFD)                      | 64 |

| 6 Fu   | nctional Operation                                      | 65 |

| 6.1    | Normal Mode                                             | 65 |

| 6.1    | .1 Memory Map Integration and Initialization            | 65 |

| 6.1    | l.2 Frame Types                                         | 66 |

| 6.1    | I.3 Rules for Messaging                                 | 67 |

| 6.1    | .4 Normal Operation                                     | 70 |

| 6.1    | 1.5 Functional Safety and Error Reporting               | 72 |

| 6.1    | 1.6 Resiliency to Error Conditions                      | 73 |

| 6.2    | Signaling                                               |    |

| 6.2    | 2.1 QoS Controls                                        | 75 |

| 6.2    | 2.2 CDC Synchronization Scheme Supported                | 76 |

| 6.2    | 2.3 Frequency Limitations for Signals                   | 76 |

| Open       | Compute Project - diPort Controller Specification Draft | 5  |

|------------|---------------------------------------------------------|----|

| 6.3        | Messages and Message Fields                             | 76 |

| 6          | S.3.1 diPort Messages for Signaling                     | 77 |

| 6          | S.3.2 diPort Messages for AXI including Flow Control    | 77 |

| 7 <i>F</i> | Appendix                                                | 94 |

| 7.1        | AXI Messages - supported and future plans               | 94 |

| 7.2        | Support for BoW PHY                                     | 95 |

|            |                                                         |    |

# 1 License

# 1.1 OCP CLA

Contributions to this Specification are made under the terms and conditions set forth in Open Compute Project Contribution License Agreement ("OCP CLA") ("Contribution License") by: NXP

You can review the signed copies of the applicable Contributor License(s) for this Specification on the OCP website at https://www.opencompute.org/legal-documents

Usage of this Specification is governed by the terms and conditions set forth in

Open Compute Project Hardware License – Permissive ("OCPHL Permissive") also known as a "Specification License".

#### Notes:

1) The following clarifications, which distinguish technology licensed in the Contribution License and/or Specification License from those technologies merely referenced (but not licensed), were accepted by the Incubation Committee of the OCP:

## [insert "None" or a description of the applicable clarifications].

2) The above license does not apply to the Appendix or Appendices. The information in the Appendix or Appendices is for reference only and non-normative in nature.

NOTWITHSTANDING THE FOREGOING LICENSES, THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN. THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE. INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO, OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION, INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 1.2 Acknowledgements

The Contributors of this Specification would like to acknowledge the following companies for their feedback:

David Kehlet, Intel

# 2 Revision Table

| Revision #                                        | Date               | Author      | Description                                                                                                                             |

|---------------------------------------------------|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| NXP definition contribution (draft)               | 24 Feb 2020 Draft  | Gary Miller | This initial release is only to provide a baseline ODSA additional                                                                      |

|                                                   |                    |             | features will be<br>provided in next<br>release                                                                                         |

| ODSA initial review feedback incorporated (draft) | 19 Jan 2021 Draft  | Gary Miller | Incorporated     extensive OSDS     feedback from     David Kruckemyer     and David Kehlet                                             |

|                                                   |                    |             | NXP considering<br>donating diPort<br>design collateral. If<br>approved, this<br>specification is<br>intended to be initial<br>version  |

|                                                   |                    |             | <ul> <li>Architected all<br/>planned future<br/>messages with<br/>future and current<br/>implementation<br/>plans documented</li> </ul> |

|                                                   |                    |             | Added registers     and simplified     process for     enabling chips from     different companies     to establish link                |

|                                                   |                    |             | Proposed BoW integration using LPIF interface                                                                                           |

| Editorial changes (draft)                         | 16 Sept 2022 Draft | Gary Miller | Editorial changes     Minor technical corrections                                                                                       |

# 3 Glossary

Controller or diPortSD Controller

The diPortSD (SD means serial data) controller is the official IP name that appears in various sections and diagrams. The name diPort controller, a shortened version, is used as well.

Device, Die and Chiplet

The diPort controller is intended for use with homogeneous and heterogeneous devices, die and chiplets. The term chip will be used in most instances to universally represent product device, die and

chiplet, whichever may be applicable.

PHY Physical interface for chip-to-chip communication. A PHY comprises logic (PCS) and analog (PMA)

portions, and one or the other may be inferred depending upon the context.

Signaling Signaling aspects include transferring any general signaling information between the two chips (e.g.,

interrupt request and system information signals).

**SiP** System in Package refers to a package with two or more chips.

**X** Bar Bus crossbar switch that provides the hardware interconnect matrix routing transactions from bus

masters to bus slaves.

# 4 Introduction

The diPortSD controller (diPort) is intended to provide a scalable chip-to-chip controller for use with homogeneous and heterogeneous devices, die as well as chiplets. The term chip will be used in most instances to universally represent product device, die and chiplet, whichever may be most applicable. There are myriads of applications such as:

- Non-coherent accesses between chips, where AXI transactions are transported. An example is accesses between two general chips, each containing local masters accessing memory mapped resources of the remote chip.

- IO coherent access, where AXI with ACE-Lite extensions are transported. An example is accesses between a main chip and

an accelerator chip. The main chip may setup the accelerator configuration to initiate a function to be accelerated. The

accelerator chip may access cached information on the main chip, and write back results when complete. When write-back

is completed, the accelerator may trigger a coherent event on the main chip using barriers to assure the main chip caches

are coherent.

#### NOTE

This version supports only non-coherent access via AXI transactions. A future specification will add ACE-Lite extensions for IO coherent accesses.

diPort is intended to add runtime processor communication and signaling between two chips. Communication aspects include ease of software access to code, data, and peripheral information between a local chip and a remote chip. Signaling aspects include access to signals between a local chip and a remote chip.

diPort resides on both chips that are interconnected via a PHY in a package. This allows for masters on either chip to access memory mapped resources on the remote chip.

As mentioned diPort supports both runtime processor communication and signaling between two chips. This arrangement works adequately unless the number of signals required or change rate of the signals becomes too high.

In a typical SiP configuration, diPort messages are transported via a PHY between two chips. Internal bus transactions on the local chip targeted to a resource on the remote chip are automatically translated and transported via diPort messages. Furthermore, the diPort bi-directionally transports signaling of necessary signal information between chips, such as system status and interrupt requests.

The diPort is latency- and bandwidth-optimized for typical master-to-peripheral access scenarios, efficiently handling single word accesses as well as burst transfers. Furthermore, another objective is to most efficiently packetize AXI transactions, using the minimum amount of AXI bus information for each of the 5 defined AXI channels, to provide the optimal latency and bandwidth between chips.

The diPort controller may be integrated directly with a PHY under certain conditions or integrated with a link layer. The diPort controller implements link layer functions intended to be used with a low error rate PHY technology. If the PHY technology has a high error rate then including FEC or integrating with a link layer with retry support is advisable.

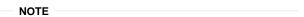

# 4.1 Block Diagram

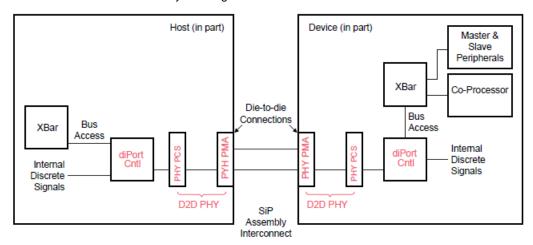

An illustration of how diPort may be integrated into SiP is shown below:

Figure 1. diPort subsystem illustration

Using parametrization diPort may be instantiated to be connected on-die to:

- AXI master

- AXI slave

- · Both AXI master and AXI slave

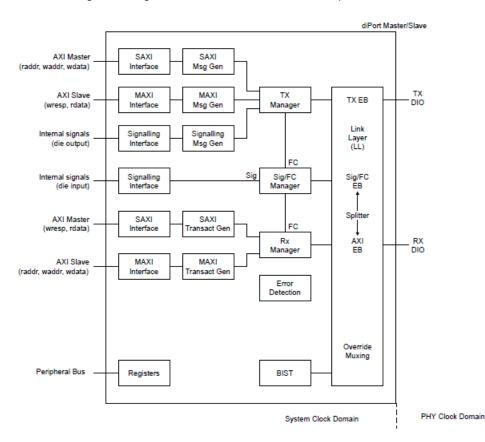

The following block diagrams illustrate a connection to a chip that acts as both AXI master and AXI slave.

Figure 2. diPort master and slave block diagram

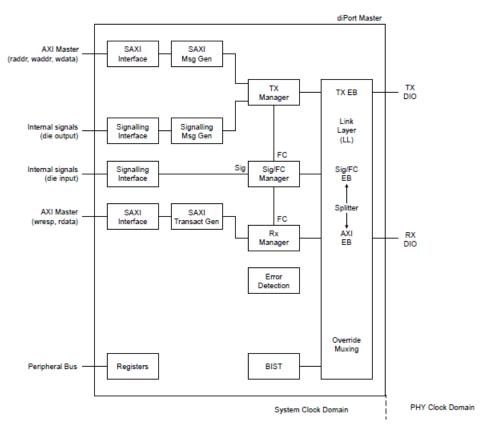

Figure 3. diPort Master block diagram

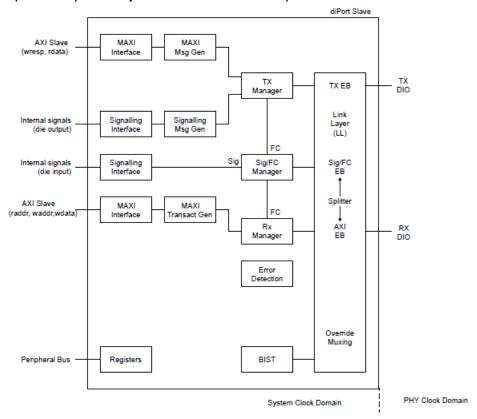

Figure 4. diPort slave block diagram

| Block             | Description                                                                                                                                                                    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| diPort            | diPort controller                                                                                                                                                              |

| DIO               | diPort chip-to-chip digital I/O                                                                                                                                                |

| SAXI Interface    | Slave AXI Interface is state logic to interface to a master's read address, write address, read data, write data and response AXI channels                                     |

| MAXI Interface    | Master AXI Interface is state logic to interface to a slave's write response read data AXI channels                                                                            |

| SAXI Msg Gen      | Slave AXI message generation logic to produce associated messages as received on read address, write address and write data AXI channels                                       |

| MAXI Msg Gen      | Master AXI message generation logic to produce associated messages as received on write response read data AXI channels                                                        |

| SAXI Transact Gen | Slave AXI message generation logic to produce associated AXI transactions as received in messages pertaining to write response and read data                                   |

| MAXI Transact Gen | Master AXI message generation logic to produce associated AXI transactions as received in messages pertaining to read address, write address and write data                    |

| TX Manager        | Manages which AXI message to transmit                                                                                                                                          |

| Sig/FC Manager    | Manages which signaling or flow control message to transmit                                                                                                                    |

| BIST              | At-speed testing through the on-die PHY pads and across chip-to-chip assembly connections                                                                                      |

| Link Layer        | Performs buffering via elasticity buffers (EB) as well as translation of physical data to logic data and vice versa. May also be connected with a link layer supporting retry. |

| RX and TX DIO     | Provides the chip-to-chip optimized I/O interface                                                                                                                              |

| Peripheral Bus    | NXP register access bus for reading and writing configuration and status registers                                                                                             |

| Sig/FC Manager    | Manages which signaling or flow control message to transmit                                                                                                                    |

Table 1. Block diagram legend

# 4.2 Features

- · Optimized for chip-to-chip communication enables ecosystem for SiPs

- · Automatic configuration of communication at start-up

- A limited amount of software configuration of register is needed for some features

- · Connected chip appears to software as on-die resources using built-in memory map address translation

- Provides a virtual interconnection of AXI bus between two chips

- Note that the current design requires the AXI bus on both chips to have the same data width

- · Supports signaling of hundreds of system states, messages, etc. between two chips

- Automatic replication on remote chip

- Supports clock-domain crossing for scalar and vectors

- Quality of service for decoupling signaling impact on AXI traffic

- Error detection, corruption prevention and resiliency (e.g., functional safety)

- · Optimized for AXI channels protocol

- Supports AXI4 plan to add support for ACE-Lite for managing IO coherency

- Tracks AXI state flow with a minimal amount of AXI attributes transferred between chips

- Minimal packetizing delays for both single and burst transactions

- Pipelining for many simultaneous reads and writes for improved latency and bandwidth

- Virtual-linked/hardware-synchronized AXI bus channels between chips

- Current design requires the AXI bus on both chips to have the same data bus width

# 4.3 Operating Modes

diPort module supports the following basic operating modes:

- Disabled

- · BIST mode

- Normal mode.

# 4.3.1 Disabled Mode

Disabled mode is used when a die mask set is not intended for use in a SiP. diPort provides for configuration via a top-level enable input, that when negated disables diPort IP. To enable diPort IP the top-level enable input must be asserted.

# 4.3.2 BIST Mode

BIST mode is entered only when test mode is enabled and a diPort BIST test mode is selected. BIST mode enables at-speed testing through the on-die micro-pads and across die-to-die assembly connections. BIST mode has a higher priority than Normal mode.

Requirements to be able to use BIST mode and BIST capabilities are:

- To use on-die loopback BIST testing, the on-die PHY must support loop back from TX to RX

- To use chip-to-chip loopback BIST testing, the remote PHY must support loop back from RX to TX

# 4.3.3 Normal Mode

AXI transactions and signaling of information between each die is fully functional.

When transitioning into Normal mode, customer software running on each of the two interconnected chips may have to provide software configuration steps to initialize diPort features, especially if the chips are from different companies. Refer to the section Memory Map Integration and Initialization

Also, refer to Normal Operation section for a detailed description of the various aspects of normal mode operation.

# 5 diPortSD register descriptions

**NOTE**

- 1. Write accesses other than 32-bit accesses are not supported. When attempted, no change is made to the register value and no transfer error is produced.

- Generally, any access to unimplemented register space results in a transfer error. This is not the case for the unimplemented register at offset 188h, which does not generate a transfer error.

# 5.1 diPortSD memory map

d\_ip\_diPort\_sd\_syn base address: 0h

| Offset | Register                                | Width     | Access | Reset value |

|--------|-----------------------------------------|-----------|--------|-------------|

|        |                                         | (In bits) |        |             |

| 100h   | Error and Control Register (ECR)        | 32        | RW     | 0000_0000h  |

| 104h   | Error Status Register (SESR)            | 32        | W1C    | 0000_0000h  |

| 108h   | Quality Of Service (QOS)                | 32        | RW     | 0000_1801h  |

| 10Ch   | Signaling Enable (SIGEN)                | 32        | RW     | 0000_0000h  |

| 118h   | Signaling Delay (SIGD)                  | 32        | RW     | 0000_0002h  |

| 11Ch   | Elasticity Buffer Configuration (EBCFG) | 32        | RW     | 0000_0000h  |

| 128h   | Logical Address Region 0 (LAR0)         | 32        | RW     | 5500_0000h  |

| 12Ch   | Physical Address Region 0 (PAR0)        | 32        | RW     | 0000_0000h  |

| 130h   | Region Size 0 (RS0)                     | 32        | RW     | 0000_000Bh  |

| 134h   | Logical Address Region 1 (LAR1)         | 32        | RW     | 5540_0000h  |

Table continues on the next page...

Table continued from the previous page...

| Offset | Register                                | Width     | Access | Reset value |

|--------|-----------------------------------------|-----------|--------|-------------|

|        |                                         | (In bits) |        |             |

| 138h   | Physical Address Region 1 (PAR1)        | 32        | RW     | 0040_0000h  |

| 13Ch   | Region Size 1 (RS1)                     | 32        | RW     | 0000_000Ah  |

| 140h   | Logical Address Region 2 (LAR2)         | 32        | RW     | 5560_0000h  |

| 144h   | Physical Address Region 2 (PAR2)        | 32        | RW     | 0060_0000h  |

| 148h   | Region Size 2 (RS2)                     | 32        | RW     | 0000_0009h  |

| 14Ch   | Logical Address Region 3 (LAR3)         | 32        | RW     | 5570_0000h  |

| 150h   | Physical Address Region 3 (PAR3)        | 32        | RW     | 0070_0000h  |

| 154h   | Region Size 3 (RS3)                     | 32        | RW     | 0000_0009h  |

| 158h   | Logical Address Region 4 (LAR4)         | 32        | RW     | 5580_0000h  |

| 15Ch   | Physical Address Region 4 (PAR4)        | 32        | RW     | 0080_0000h  |

| 160h   | Region Size 4 (RS4)                     | 32        | RW     | 0000_000Ch  |

| 164h   | Logical Address Region 5 (LAR5)         | 32        | RW     | 5600_0000h  |

| 168h   | Physical Address Region 5 (PAR5)        | 32        | RW     | 2000_0000h  |

| 16Ch   | Region Size 5 (RS5)                     | 32        | RW     | 0000_000Ch  |

| 170h   | Logical Address Region 6 (LAR6)         | 32        | RW     | 5680_0000h  |

| 174h   | Physical Address Region 6 (PAR6)        | 32        | RW     | 4000_0000h  |

| 178h   | Region Size 6 (RS6)                     | 32        | RW     | 0000_000Ch  |

| 17Ch   | Logical Address Region 7 (LAR7)         | 32        | RW     | 0000_0000h  |

| 180h   | Physical Address Region 7 (PAR7)        | 32        | RW     | 0000_0000h  |

| 184h   | Region Size 7 (RS7)                     | 32        | RW     | 0000_0000h  |

| 188h   | Logical Address Region Upper 0 (LARU0)  | 32        | RW     | 5500_0000h  |

| 18Ch   | Physical Address Region Upper 0 (PARU0) | 32        | RW     | 5500_0000h  |

| 190h   | Logical Address Region Upper 1 (LARU1)  | 32        | RW     | 5540_0000h  |

| 194h   | Physical Address Region Upper 1 (PARU1) | 32        | RW     | 5540_0000h  |

| 198h   | Logical Address Region Upper 2 (LARU2)  | 32        | RW     | 5560_0000h  |

| 19Ch   | Physical Address Region Upper 2 (PARU2) | 32        | RW     | 5560_0000h  |

| 1A0h   | Logical Address Region Upper 3 (LARU3)  | 32        | RW     | 5570_0000h  |

| 1A4h   | Physical Address Region Upper 3 (PARU3) | 32        | RW     | 5570_0000h  |

| 1A8h   | Logical Address Region Upper 4 (LARU4)  | 32        | RW     | 5580_0000h  |

| 1ACh   | Physical Address Region Upper 4 (PARU4) | 32        | RW     | 5580_0000h  |

| 1B0h   | Logical Address Region Upper 5 (LARU5)  | 32        | RW     | 5600_0000h  |

Table continues on the next page...

Table continued from the previous page...

| Offset | Register                                | Width     | Access | Reset value |

|--------|-----------------------------------------|-----------|--------|-------------|

|        |                                         | (In bits) |        |             |

| 1B4h   | Physical Address Region Upper 5 (PARU5) | 32        | RW     | 5600_0000h  |

| 1B8h   | Logical Address Region Upper 6 (LARU6)  | 32        | RW     | 5680_0000h  |

| 1BCh   | Physical Address Region Upper 6 (PARU6) | 32        | RW     | 5680_0000h  |

| 1C0h   | Logical Address Region Upper 7 (LARU7)  | 32        | RW     | 0000_0000h  |

| 1C4h   | Physical Address Region Upper 7 (PARU7) | 32        | RW     | 0000_0000h  |

| 200h   | BIST Control and Pattern (BIST_CP)      | 32        | RW     | 0000_0000h  |

| 204h   | BIST Status (BIST_ST)                   | 32        | RO     | 0000_0000h  |

| 208h   | BIST Failures (BIST_FLS)                | 32        | RO     | 0000_0000h  |

| 20Ch   | BIST Upper Failing Data (BIST_UFD)      | 32        | RO     | 0000_0000h  |

| 210h   | BIST Lower Failing Data (BIST_LFD)      | 32        | RO     | 0000_0000h  |

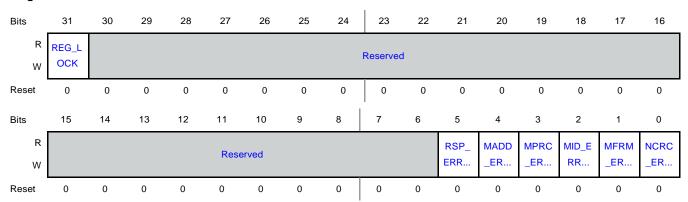

# 5.2 Error and Control Register (ECR)

## Offset

| Register | Offset |

|----------|--------|

| ECR      | 100h   |

#### **Function**

The ECR is used for general control bits as well as to enable the error signal outputs of the diPortSD module. This register is initialized by resetting the controller.

| Field      | Function                                                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 31         | Register Lock                                                                                                                                    |

| REG_LOCK   | The set-once control bit locks the contents of selected configuration registers when set. The control bit is cleared by reseting the controller. |

|            | 0b - When cleared at reset, writes can update contents of LAR, PAR, SIGD and BIST registers.                                                     |

|            | 1b - When set, locks the contents of LAR, PAR, SIGD and BIST registers.                                                                          |

| 30-6       | Reserved                                                                                                                                         |

| _          |                                                                                                                                                  |

| 5          | Response Error Enable                                                                                                                            |

| RSP_ERR_EN | 0b - No error signal is generated                                                                                                                |

|            | 1b - Detection of response error generates an error signal                                                                                       |

| 4          | Message Address Error Enable                                                                                                                     |

| MADD_ERR_E | 0b - No error signal is generated                                                                                                                |

| N          | 1b - Detection of response error generates an error signal                                                                                       |

| 3          | Message Processing Error Enable                                                                                                                  |

| MPRC_ERR_E | 0b - No error signal is generated                                                                                                                |

| N          | 1b - Detection of message processing error generates an error signal                                                                             |

| 2          | Message ID Error Enable                                                                                                                          |

| MID_ERR_EN | 0b - No error signal is generated                                                                                                                |

|            | 1b - Detection of message ID error generates an error signal                                                                                     |

| 1          | Message Frame Error Enable                                                                                                                       |

| MFRM_ERR_E | 0b - No error signal is generated                                                                                                                |

| N          | 1b - Detection of message frame error generates an error signal                                                                                  |

| 0          | Normal Mode CRC Error Enable                                                                                                                     |

| NCRC_ERR_E | 0b - No error signal is generated                                                                                                                |

| N          | 1b - Detection of Normal mode CRC error generates an error signal                                                                                |

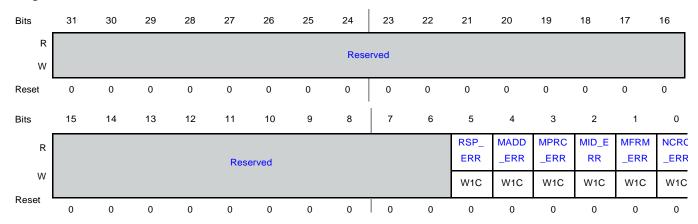

# 5.3 Error Status Register (SESR)

## Offset

| Register | Offset |

|----------|--------|

| SESR     | 104h   |

## **Function**

The SESR indicates the occurrence of an error due to a random hardware fault. This register is initialized by reseting the controller.

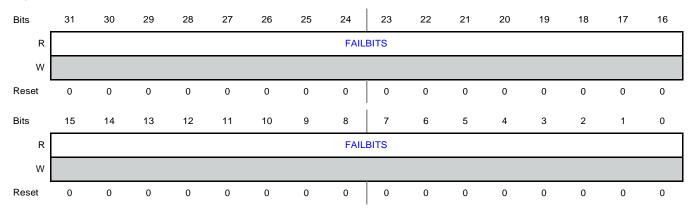

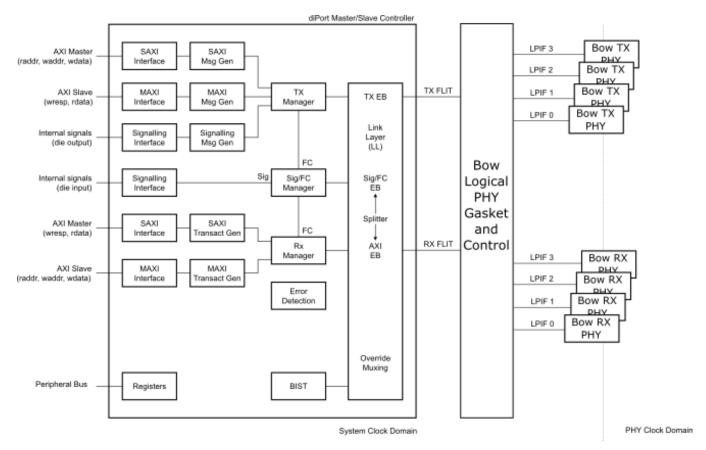

# Diagram

## **Fields**

| Field    | Function                                                                                                                                                                                                                                                                                          |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-6     | Reserved                                                                                                                                                                                                                                                                                          |

| _        |                                                                                                                                                                                                                                                                                                   |

| 5        | Response Error Status                                                                                                                                                                                                                                                                             |

| RSP_ERR  | If, due to a random hardware fault, the remote chiplet does not respond as expected to an AXI message (i.e., not sending write acknowledge back), this error condition is detected.                                                                                                               |

|          | 0b - Cleared by writing logic 1                                                                                                                                                                                                                                                                   |

|          | 1b - Set when a response error is detected during Normal mode                                                                                                                                                                                                                                     |

| 4        | Message Address Error Status                                                                                                                                                                                                                                                                      |

| MADD_ERR | A message address error may occur due to a random hardware fault. This pertains to the ARADDR and AWADDR fields in read and write address messages. These fields are checked at the remote chiplet to assure that after transport they properly reside within the physical address space defined. |

|          | 0b - Cleared by writing logic 1                                                                                                                                                                                                                                                                   |

|          | 1b - Set when a message address error is detected during Normal mode                                                                                                                                                                                                                              |

| 3        | Message Processing Error Status                                                                                                                                                                                                                                                                   |

| MPRC_ERR | A message processing error may occur due to a random hardware fault. A message processing error is detected if anywhere along the data path from the physical to logic there is a FIFO overrun.                                                                                                   |

|          | 0b - Cleared by writing logic 1                                                                                                                                                                                                                                                                   |

|          | 1b - Set when a message error is reported during Normal mode                                                                                                                                                                                                                                      |

Table continues on the next page...

Table continued from the previous page...

| Field    | Function                                                                                                                                                                                                                                     |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2        | Message ID Error Status                                                                                                                                                                                                                      |  |  |  |

| MID_ERR  | A message identification error may occur due to a random hardware fault. This pertains to the MID field in each message used to identify message type and form. A message ID error occurs if the message ID is not registered as a valid ID. |  |  |  |

|          | 0b - Cleared by writing logic 1                                                                                                                                                                                                              |  |  |  |

|          | 1b - Set when a message ID error is reported during Normal mode                                                                                                                                                                              |  |  |  |

| 1        | Message Frame Error Status                                                                                                                                                                                                                   |  |  |  |

| MFRM_ERR | A message frame error may occur due to a random hardware fault. A framing error is detected if the message form is not correct due to an incomplete number of message bytes received.                                                        |  |  |  |

|          | 0b - Cleared by writing logic 1                                                                                                                                                                                                              |  |  |  |

|          | 1b - Set when a message frame error is reported during Normal mode                                                                                                                                                                           |  |  |  |

| 0        | Normal Mode CRC Error Status                                                                                                                                                                                                                 |  |  |  |

| NCRC_ERR | A CRC error may be detected due to a random hardware fault.                                                                                                                                                                                  |  |  |  |

|          | 0b - Cleared by writing logic 1                                                                                                                                                                                                              |  |  |  |

|          | 1b - Set when a CRC error is reported during Normal mode                                                                                                                                                                                     |  |  |  |

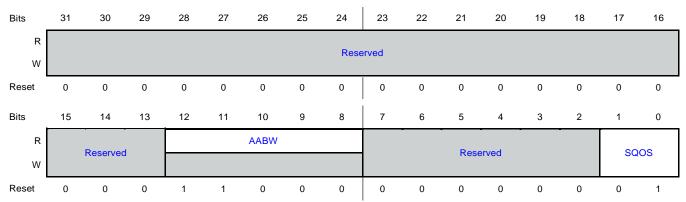

# 5.3 Quality Of Service (QOS)

## Offset

| Register | Offset |

|----------|--------|

| QOS      | 108h   |

## **Function**

This register is used for over-riding the QOS selected parameter setting. This register is initialized by reseting the controller.

| Field | Function                                                                                                                                                                                                                    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-13 | Reserved                                                                                                                                                                                                                    |

| _     |                                                                                                                                                                                                                             |

| 12-8  | Active AXI Bandwidth                                                                                                                                                                                                        |

| AABW  | The AABW field provides the active or instantaneous calculation for AXI bandwidth over the last 24 double bytes of controller message generation. The range is 0 to 24 where each count represents 4.166% of AXI bandwidth. |

| 7-2   | Reserved                                                                                                                                                                                                                    |

| _     |                                                                                                                                                                                                                             |

| 1-0   | Quality of Service                                                                                                                                                                                                          |

| sqos  | The SQOS field allows for software to override the SQoS setting described in the Signaling section.                                                                                                                         |

|       | 00b - Change to 50% bandwidth to both AXI and Signaling messages                                                                                                                                                            |

|       | 01b - Change to 75% bandwidth to AXI messages and 25% bandwidth to Signaling messages                                                                                                                                       |

|       | 10b - Change to 87.5% bandwidth to AXI messages and 12.5% bandwidth to Signaling messages                                                                                                                                   |

|       | 11b - Change to 100% bandwidth to AXI messages                                                                                                                                                                              |

# 5.4 Signaling Enable (SIGEN)

#### Offset

| Register | Offset |

|----------|--------|

| SIGEN    | 10Ch   |

#### **Function**

This register is used for overriding the settings. This register is initialized by reseting the controller. When set, it enables signaling events (for example, signal state transition) input to the diPortSD to be detected on the local chiplet where SIGEN was set. Once detected, the resultant signal state is mirrored on the remote chiplet via a signaling message that is transported between chiplets. An initialization process is initiated when first set, in order to initialize states on the remote chiplet. To enable signaling events on both chiplets, the SIGEN register must be set on both chiplets. Note that signaling should only be enabled after all diPort related clock frequencies on both chiplets are fully ramped.

## Diagram

| Bits   | 31       | 30 | 29 | 28 | 27 | 26 | 25 | 24   | 23    | 22 | 21  | 20 | 19 | 18 | 17 | 16 |

|--------|----------|----|----|----|----|----|----|------|-------|----|-----|----|----|----|----|----|

| R<br>W |          |    |    |    |    |    |    | Rese | erved |    |     |    |    |    |    |    |

| Reset  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0  | 0  |

| Bits   | 15       | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7     | 6  | 5   | 4  | 3  | 2  | 1  | 0  |

| R<br>W | Reserved |    |    |    |    |    |    |      |       |    | SIG | EN |    |    |    |    |

| Reset  | 0        | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0     | 0  | 0   | 0  | 0  | 0  | 0  | 0  |

## **Fields**

| Field | Function                                                                                                                                                            |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 31-8  | Reserved                                                                                                                                                            |  |  |

| _     |                                                                                                                                                                     |  |  |

| 7-0   | Signaling Enable                                                                                                                                                    |  |  |

| SIGEN | This field is used for over-riding the default SIGEN setting. This register is initialized by reseting the controller. If written to 0xFF all signaling is enabled. |  |  |

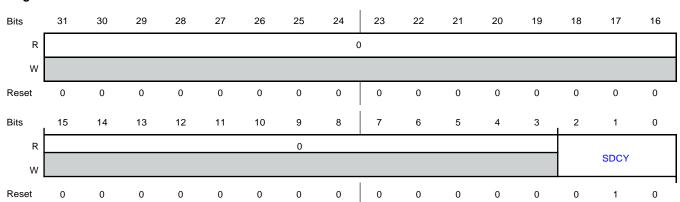

# 5.5 Signaling Delay (SIGD)

## Offset

| Register | Offset |

|----------|--------|

| SIGD     | 118h   |

#### **Function**

Use this register to specify the number of AXI bus clocks between signaling messages.

| Field       | Function                                                                                                                                                                                                                                                                                                                 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-3        | Reserved                                                                                                                                                                                                                                                                                                                 |

| _           |                                                                                                                                                                                                                                                                                                                          |

| 2-0<br>SDCY | Signaling Delay Cycles. This field defines the number of AXI bus clocks between signaling messages. The setting provides a bandwidth limit to signaling messages and is applied when there are no competing requests for AXI messages. It assures signaling messages do not exceed 50 % of total diPortSD bus bandwidth. |

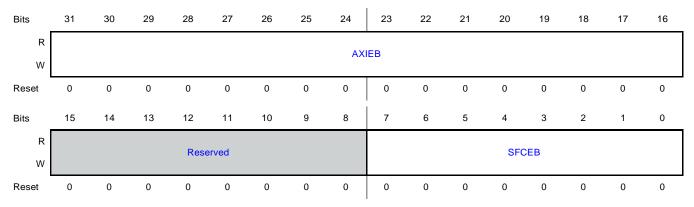

# 5.6 Elasticity Buffer Configuration (EBCFG)

## Offset

| Register | Offset |

|----------|--------|

| EBCFG    | 11Ch   |

#### **Function**

Use this register to read the implemented size for the AXI and Signaling/FC Elasticity Buffers and re-configure if needed. The reset values indicate the implemented size for each elasticity buffer. The size for each buffer may be reduced as needed to match the size for the corresponding elasticity buffer on the remote chiplet. The AXI and Signaling/FC Elasticity Buffer sizes for both chiplets must be set to match to assure proper operation.

| Field | Function                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-16 | AXI Elasticity Buffer                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AXIEB | This field is used for reading the implemented size for the AXI Elasticity Buffer and for re-configuring the size if needed to match the remote chiplets buffer size. The reset value indicates the implemented size, which may be reduced as needed to match the size for the corresponding elasticity buffer on the remote chiplet. The size may not be increased beyond the reset value. The field represents the size in double bytes.         |

| 15-8  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7-0   | Signaling/FC Elasticity Buffer                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SFCEB | This field is used for reading the implemented size for the Signaling/FC Elasticity Buffer and for reconfiguring the size if needed to match the remote chiplets buffer size. The reset value indicates the implemented size, which may be reduced as needed to match the size for the corresponding elasticity buffer on the remote chiplet. The size may not be increased beyond the reset value. The field represents the size in double bytes. |

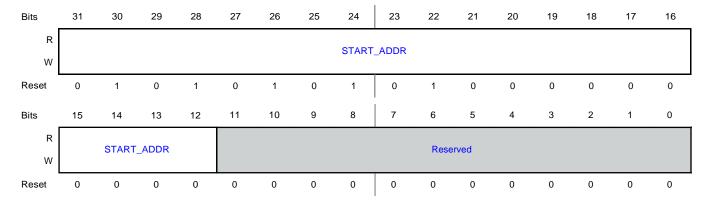

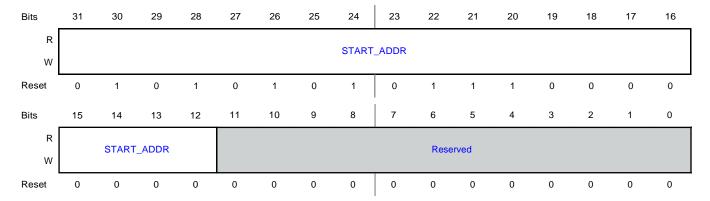

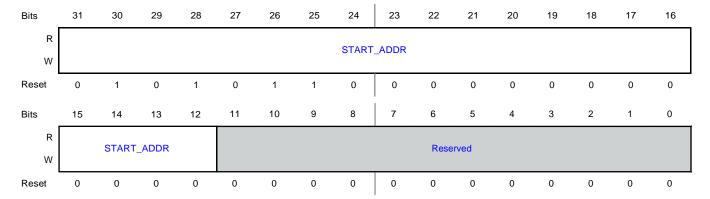

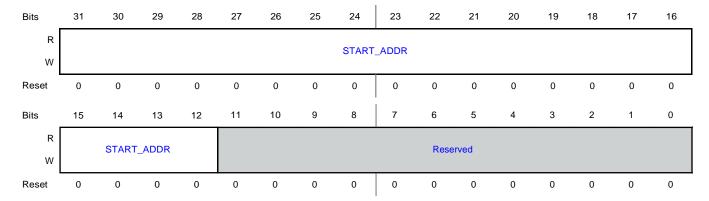

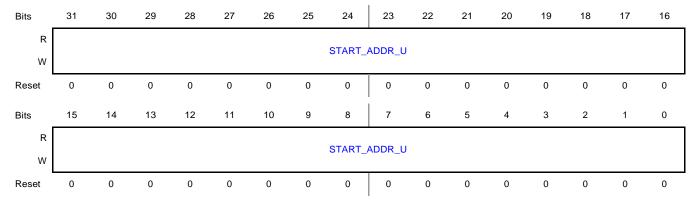

# 5.7 Logical Address Region 0 (LAR0)

## Offset

| Register | Offset |

|----------|--------|

| LAR0     | 128h   |

#### **Function**

The LAR registers define base address bits [31:12] of the logical address of the expansion regions. Depending upon the setting of BLOCK\_SIZE, a specific number of lower order bits of LAR must be set to zero. This register is only accessible when device parameterization enables AXI master capability.

| Field      | Function                                                                                     |

|------------|----------------------------------------------------------------------------------------------|

| 31-12      | Starting Logical Address for Expansion Region 0                                              |

| START_ADDR | The START_ADDR field defines the logical start address bits [31:12] of the expansion region. |

| 11-0       | Reserved                                                                                     |

| _          |                                                                                              |

# 5.8 Physical Address Region 0 (PAR0)

#### Offset

| Register | Offset |

|----------|--------|

| PAR0     | 12Ch   |

#### **Function**

The PAR registers define base address bits [31:12] of the physical address of the expansion regions. Depending upon the setting of BLOCK\_SIZE, a specific number of lower order bits of PAR must be set to zero. This register is only accessible when device parameterization enables AXI master capability. Note that the values for the Physical Address Region registers must match the remote chiplet's parameters for physical address regions. If they do not, address errors are generated and the transactions dropped.

## Diagram

#### **Fields**

| Field      | Function                                                                                      |

|------------|-----------------------------------------------------------------------------------------------|

| 31-12      | Starting Physical Address for Expansion Region 0                                              |

| START_ADDR | The START_ADDR field defines the physical start address bits [31:12] of the expansion region. |

| 11-0       | Reserved                                                                                      |

| _          |                                                                                               |

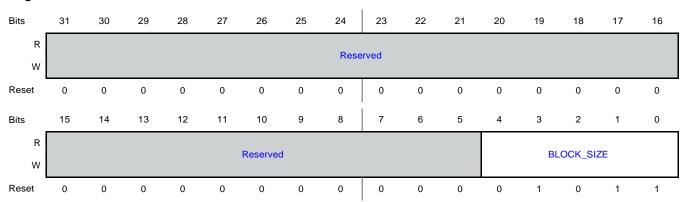

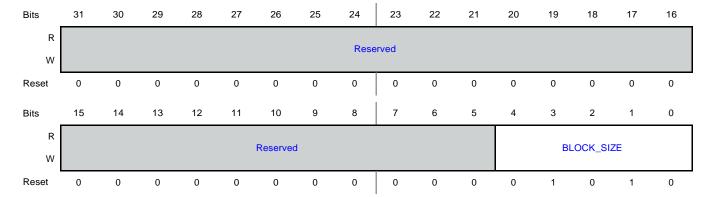

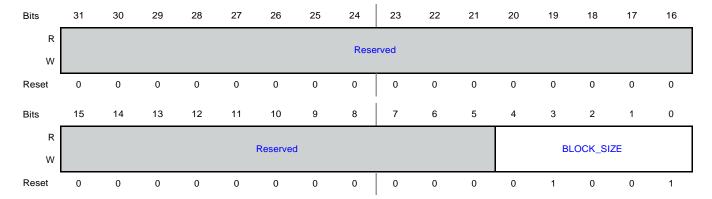

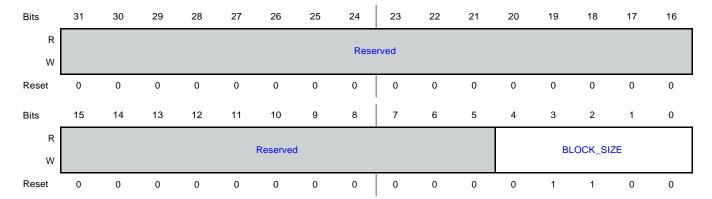

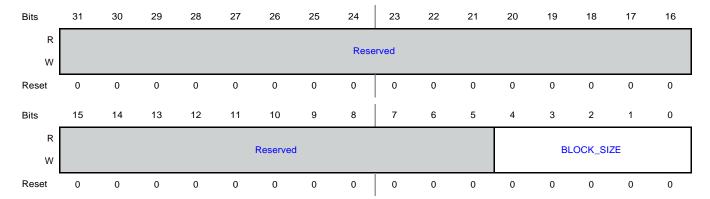

# 5.9 Region Size 0 (RS0)

#### Offset

| Register | Offset |

|----------|--------|

| RS0      | 130h   |

#### **Function**

Normally there is no need to write the Region Size registers, unless the reset value is not adequate. The reset values for the Region Size registers are defined at design instance using the RDSZ0 to RDSZ7 parameters. Note that the values for the Region Size registers must match the remote chiplet's parameters for region sizes. If they do not, address errors are generated and the transaction dropped. The BLOCK\_SIZE field defines the block size of the associated expansion region. This register is only accessible when device parameterization enables AXI master capability.

## Diagram

#### **Fields**

| Field | Function |

|-------|----------|

| 31-5  | Reserved |

| _     |          |

Table continues on the next page...

Table continued from the previous page...

| Field      | Function                                                                                                                                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-0        | Block Size of the Expansion Address Region 0                                                                                                                            |

| BLOCK_SIZE | BLOCK_SIZE determines the size of the region. Depending upon the setting, as described below, a specific number of lower order bits of LAR and PAR must be set to zero. |

|            | 00000b - Zero size region                                                                                                                                               |

|            | 00001b - 4 KB block size. Lower 12 bits of associated START_ADDR must be zero.                                                                                          |

|            | 00010b - 8 KB block size. Lower 13 bits of associated START_ADDR must be zero.                                                                                          |

|            | 00011b - 16 KB block size. Lower 14 bits of associated START_ADDR must be zero.                                                                                         |

|            | 00100b - 32 KB block size. Lower 15 bits of associated START_ADDR must be zero.                                                                                         |

|            | 00101b - 64 KB block size. Lower 16 bits of associated START_ADDR must be zero.                                                                                         |

|            | 00110b - 128 KB block size. Lower 17 bits of associated START_ADDR must be zero.                                                                                        |

|            | 00111b - 256 KB block size. Lower 18 bits of associated START_ADDR must be zero.                                                                                        |

|            | 01000b - 512 KB block size. Lower 19 bits of associated START_ADDR must be zero.                                                                                        |

|            | 01001b - 1 MB block size. Lower 20 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01010b - 2 MB block size. Lower 21 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01011b - 4 MB block size. Lower 22 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01100b - 8 MB block size. Lower 23 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01101b - 16 MB block size. Lower 24 bits of associated START_ADDR must be zero.                                                                                         |

|            | 01110b - 32 MB block size. Lower 25 bits of associated START_ADDR must be zero.                                                                                         |

|            | 01111b - 64 MB block size. Lower 26 bits of associated START_ADDR must be zero.                                                                                         |

|            | 10000b - 128 MB block size. Lower 27 bits of associated START_ADDR must be zero.                                                                                        |

|            | 10001b - 256 MB block size. Lower 28 bits of associated START_ADDR must be zero.                                                                                        |

|            | 10010b - 512 MB block size. Lower 29 bits of associated START_ADDR must be zero.                                                                                        |

|            | 10011b - 1 GB block size. Lower 30 bits of associated START_ADDR must be zero.                                                                                          |

|            | 10100b - 2 GB block size. Lower 31 bits of associated START_ADDR must be zero.                                                                                          |

# 5.10 Logical Address Region 1 (LAR1)

## Offset

| Register | Offset |

|----------|--------|

| LAR1     | 134h   |

#### **Function**

The LAR registers define base address bits [31:12] of the logical address of the expansion regions. Depending upon the setting of BLOCK\_SIZE, a specific number of lower order bits of LAR must be set to zero. This register is only accessible when device parameterization enables AXI master capability.

| Field      | Function                                                                                     |

|------------|----------------------------------------------------------------------------------------------|

| 31-12      | Starting Logical Address for Expansion Region 1                                              |

| START_ADDR | The START_ADDR field defines the logical start address bits [31:12] of the expansion region. |

| 11-0       | Reserved                                                                                     |

| _          |                                                                                              |

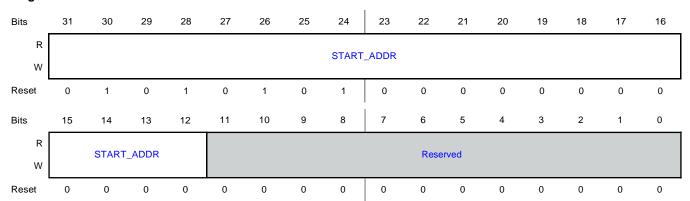

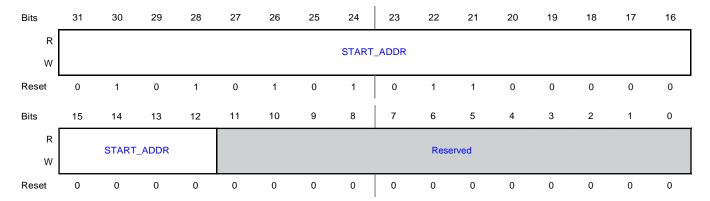

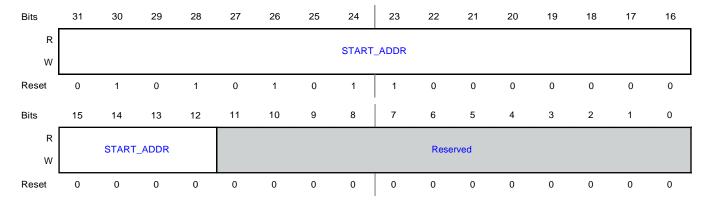

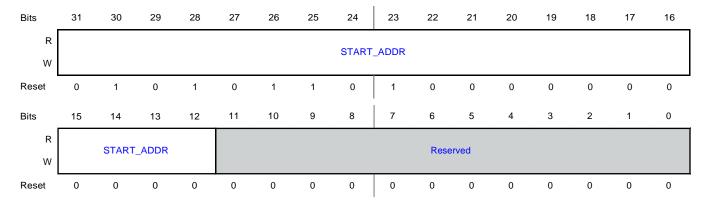

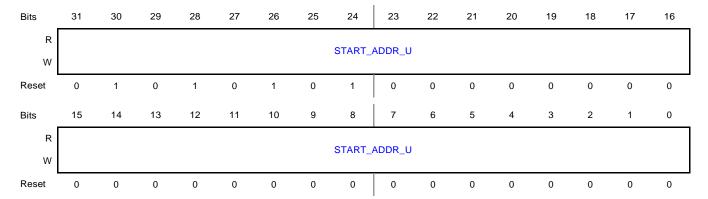

# 5.11 Physical Address Region 1 (PAR1)

## Offset

| Register | Offset |

|----------|--------|

| PAR1     | 138h   |

#### **Function**

The PAR registers define base address bits [31:12] of the physical address of the expansion regions. Depending upon the setting of BLOCK\_SIZE, a specific number of lower order bits of PAR must be set to zero. This register is only accessible when device parameterization enables AXI master capability. Note that the values for the Physical Address Region registers must match the remote chiplet's parameters for physical address regions. If they do not, address errors are generated and the transactions dropped.

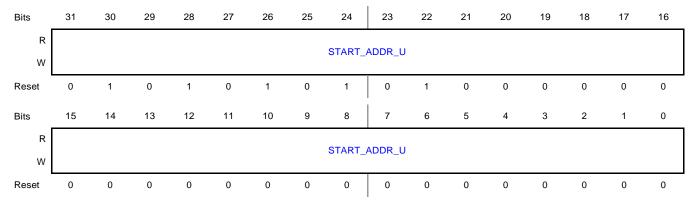

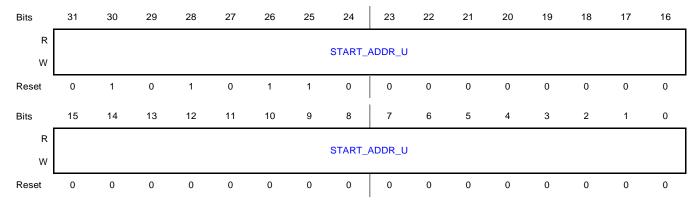

#### Diagram

| Bits   | 31         | 30 | 29 | 28 | 27 | 26 | 25 | 24    | 23    | 22   | 21 | 20 | 19 | 18 | 17 | 16 |

|--------|------------|----|----|----|----|----|----|-------|-------|------|----|----|----|----|----|----|

| R<br>W |            |    |    |    |    |    |    | START | _ADDR |      |    |    |    |    |    |    |

| Reset  | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0     | 1    | 0  | 0  | 0  | 0  | 0  | 0  |

| Bits   | 15         | 14 | 13 | 12 | 11 | 10 | 9  | 8     | 7     | 6    | 5  | 4  | 3  | 2  | 1  | 0  |

| R<br>W | START_ADDR |    |    |    |    |    |    |       | Rese  | rved |    |    |    |    |    |    |

| Reset  | 0          | 0  | 0  | 0  | 0  | 0  | 0  | 0     | 0     | 0    | 0  | 0  | 0  | 0  | 0  | 0  |

#### **Fields**

| Field      | Function                                                                                      |

|------------|-----------------------------------------------------------------------------------------------|

| 31-12      | Starting Physical Address for Expansion Region 1                                              |

| START_ADDR | The START_ADDR field defines the physical start address bits [31:12] of the expansion region. |

| 11-0       | Reserved                                                                                      |

| _          |                                                                                               |

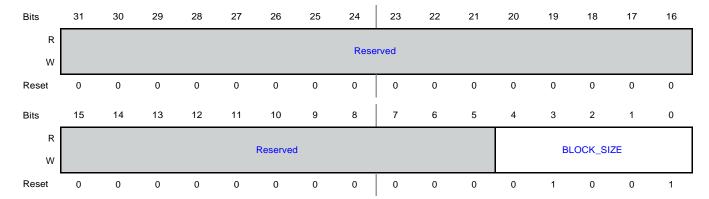

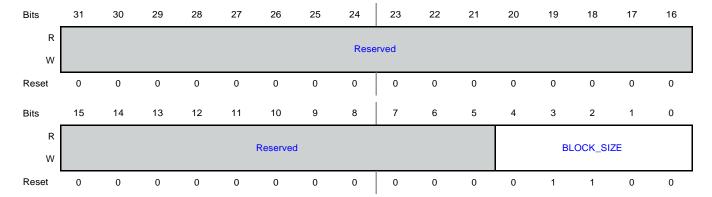

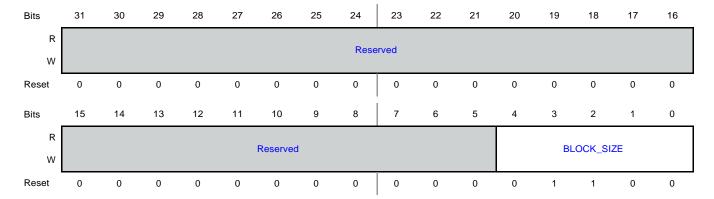

# 5.12 Region Size 1 (RS1)

#### Offset

| Register | Offset |

|----------|--------|

| RS1      | 13Ch   |

#### **Function**

Normally there is no need to write the Region Size registers, unless the reset value is not adequate. The reset values for the Region Size registers are defined at design instance using the RDSZ0 to RDSZ7 parameters. Note that the values for the Region Size registers must match the remote chiplet's parameters for region sizes. If they do not, address errors are generated and the transaction dropped. The BLOCK\_SIZE field defines the block size of the associated expansion region. This register is only accessible when device parameterization enables AXI master capability.

| Field | Function |

|-------|----------|

| 31-5  | Reserved |

| _     |          |

Table continues on the next page...

Table continued from the previous page...

| Field      | Function                                                                                                                                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-0        | Block Size of the Expansion Address Region 1                                                                                                                            |

| BLOCK_SIZE | BLOCK_SIZE determines the size of the region. Depending upon the setting, as described below, a specific number of lower order bits of LAR and PAR must be set to zero. |

|            | 00000b - Zero size region                                                                                                                                               |

|            | 00001b - 4 KB block size. Lower 12 bits of associated START_ADDR must be zero.                                                                                          |

|            | 00010b - 8 KB block size. Lower 13 bits of associated START_ADDR must be zero.                                                                                          |

|            | 00011b - 16 KB block size. Lower 14 bits of associated START_ADDR must be zero.                                                                                         |

|            | 00100b - 32 KB block size. Lower 15 bits of associated START_ADDR must be zero.                                                                                         |

|            | 00101b - 64 KB block size. Lower 16 bits of associated START_ADDR must be zero.                                                                                         |

|            | 00110b - 128 KB block size. Lower 17 bits of associated START_ADDR must be zero.                                                                                        |

|            | 00111b - 256 KB block size. Lower 18 bits of associated START_ADDR must be zero.                                                                                        |

|            | 01000b - 512 KB block size. Lower 19 bits of associated START_ADDR must be zero.                                                                                        |

|            | 01001b - 1 MB block size. Lower 20 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01010b - 2 MB block size. Lower 21 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01011b - 4 MB block size. Lower 22 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01100b - 8 MB block size. Lower 23 bits of associated START_ADDR must be zero.                                                                                          |

|            | 01101b - 16 MB block size. Lower 24 bits of associated START_ADDR must be zero.                                                                                         |

|            | 01110b - 32 MB block size. Lower 25 bits of associated START_ADDR must be zero.                                                                                         |

|            | 01111b - 64 MB block size. Lower 26 bits of associated START_ADDR must be zero.                                                                                         |

|            | 10000b - 128 MB block size. Lower 27 bits of associated START_ADDR must be zero.                                                                                        |

|            | 10001b - 256 MB block size. Lower 28 bits of associated START_ADDR must be zero.                                                                                        |

|            | 10010b - 512 MB block size. Lower 29 bits of associated START_ADDR must be zero.                                                                                        |

|            | 10011b - 1 GB block size. Lower 30 bits of associated START_ADDR must be zero.                                                                                          |

|            | 10100b - 2 GB block size. Lower 31 bits of associated START_ADDR must be zero.                                                                                          |

# 5.13 Logical Address Region 2 (LAR2)

## Offset

| Register | Offset |

|----------|--------|

| LAR2     | 140h   |

#### **Function**

The LAR registers define base address bits [31:12] of the logical address of the expansion regions. Depending upon the setting of BLOCK\_SIZE, a specific number of lower order bits of LAR must be set to zero. This register is only accessible when device parameterization enables AXI master capability.

| Field      | Function                                                                                     |

|------------|----------------------------------------------------------------------------------------------|

| 31-12      | Starting Logical Address for Expansion Region 2                                              |

| START_ADDR | The START_ADDR field defines the logical start address bits [31:12] of the expansion region. |

| 11-0       | Reserved                                                                                     |

| _          |                                                                                              |

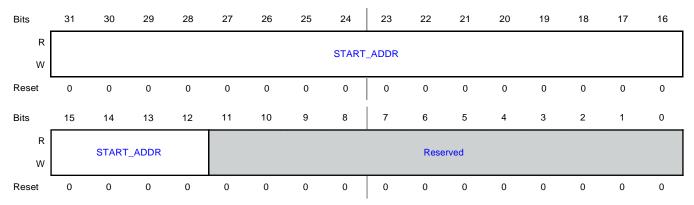

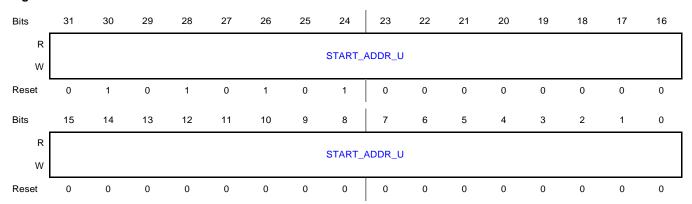

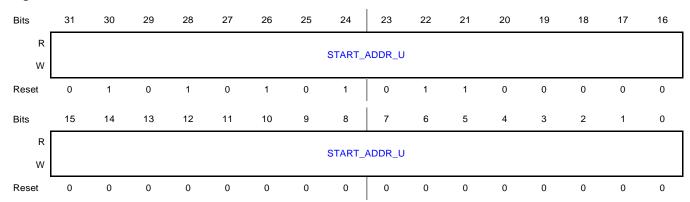

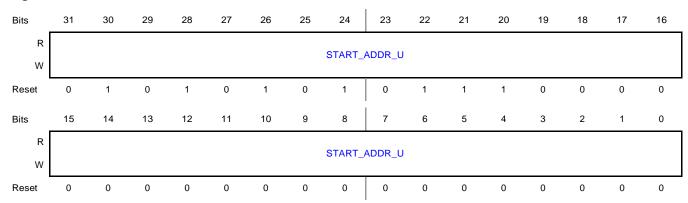

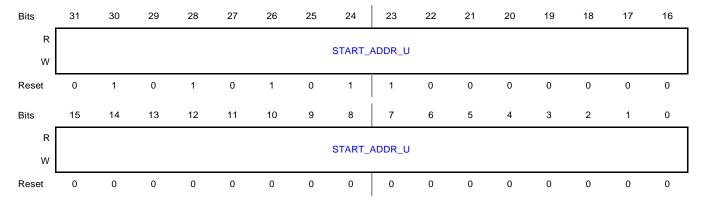

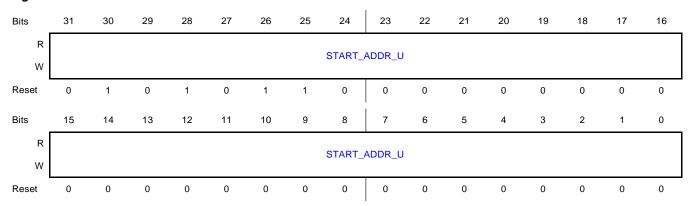

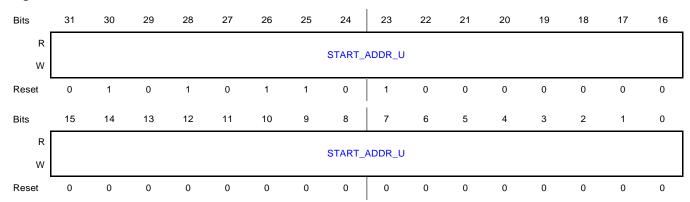

# 5.14 Physical Address Region 2 (PAR2)

## Offset

| Register | Offset |

|----------|--------|

| PAR2     | 144h   |

#### **Function**

The PAR registers define base address bits [31:12] of the physical address of the expansion regions. Depending upon the setting of BLOCK\_SIZE, a specific number of lower order bits of PAR must be set to zero. This register is only accessible when device parameterization enables AXI master capability. Note that the values for the Physical Address Region registers must match the remote chiplet's parameters for physical address regions. If they do not, address errors are generated and the transactions dropped.

#### Diagram

| Bits   | 31         | 30    | 29    | 28 | 27  | 26 | 25 | 24   | 23   | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|--------|------------|-------|-------|----|-----|----|----|------|------|----|----|----|----|----|----|----|

| R<br>W | START_ADDR |       |       |    |     |    |    |      |      |    |    |    |    |    |    |    |

| Reset  | 0          | 0     | 0     | 0  | 0   | 0  | 0  | 0    | 0    | 1  | 1  | 0  | 0  | 0  | 0  | 0  |

| Bits   | 15         | 14    | 13    | 12 | 11  | 10 | 9  | 8    | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| R<br>W |            | START | _ADDR |    | Res |    |    | Rese | rved |    |    |    |    |    |    |    |

| Reset  | 0          | 0     | 0     | 0  | 0   | 0  | 0  | 0    | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

#### **Fields**

| Field      | Function                                                                                      |

|------------|-----------------------------------------------------------------------------------------------|

| 31-12      | Starting Physical Address for Expansion Region 2                                              |

| START_ADDR | The START_ADDR field defines the physical start address bits [31:12] of the expansion region. |

| 11-0       | Reserved                                                                                      |

| _          |                                                                                               |

# 5.15 Region Size 2 (RS2)

## Offset

| Register | Offset |

|----------|--------|

| RS2      | 148h   |

#### **Function**

Normally there is no need to write the Region Size registers, unless the reset value is not adequate. The reset values for the Region Size registers are defined at design instance using the RDSZ0 to RDSZ7 parameters. Note that the values for the Region Size registers must match the remote chiplet's parameters for region sizes. If they do not, address errors are generated and the transaction dropped. The BLOCK\_SIZE field defines the block size of the associated expansion region. This register is only accessible when device parameterization enables AXI master capability.

| Field | Function |

|-------|----------|

| 31-5  | Reserved |

| _     |          |

Table continues on the next page...

Table continued from the previous page...

| Field      | Function                                                                                                                                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-0        | Block Size of the Expansion Address Region 2                                                                                                                            |

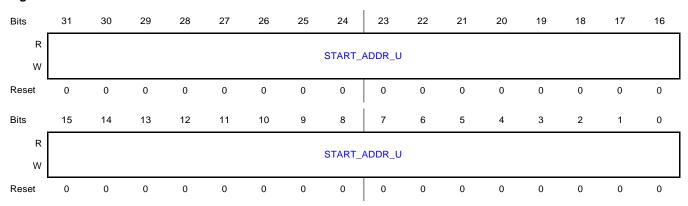

| BLOCK_SIZE | BLOCK_SIZE determines the size of the region. Depending upon the setting, as described below, a specific number of lower order bits of LAR and PAR must be set to zero. |